# UM0560 User manual

STM8 bootloader

#### Introduction

This document describes the features and operation of the STM8 integrated bootloader program STSW-STM8068. This code embedded in the system memory of the device (ROM memory) allows memories, including Flash program memory, data EEPROM and RAM, to be written into the device using the standard serial interfaces LINUART/UART/USART, SPI and CAN.

The bootloader code is similar for all STM8 versions. However, even though a peripheral may be present in a product, the product may not support it (for example the SPI is not supported in 128-Kbyte devices). In addition, different STM8 device types support different peripherals (see *Table 5: Serial interfaces associated with STM8 devices* for detailed information).

For further information on the STM8 family features, pinout, electrical characteristics, mechanical data and ordering information, refer to the STM8 datasheets.

Contents UM0560

# **Contents**

| 1 | Boo  | Bootloader introduction |                                                  |    |

|---|------|-------------------------|--------------------------------------------------|----|

|   | 1.1  | Bootlo                  | ader activation                                  | 7  |

| 2 | Peri | pheral s                | settings                                         | 12 |

|   | 2.1  | USAR                    | T/UARTs settings                                 | 12 |

|   |      | 2.1.1                   | LINUART/UARTs in "reply" mode settings           | 13 |

|   | 2.2  | SPI se                  | ettings                                          | 13 |

|   | 2.3  | CAN s                   | settings                                         | 14 |

| 3 | Boo  | tloader                 | command set                                      | 16 |

|   | 3.1  | Get co                  | ommand                                           | 17 |

|   |      | 3.1.1                   | Get command via USART/LINUART/UART1/ UART2/UART3 | 17 |

|   |      | 3.1.2                   | Get command via SPI                              | 19 |

|   |      | 3.1.3                   | Get command via CAN                              | 21 |

|   | 3.2  | 3.2 Read memory command |                                                  | 23 |

|   |      | 3.2.1                   | Read memory command via USART/LINUART/UART1/2/3  | 23 |

|   |      | 3.2.2                   | Read memory command via SPI                      | 25 |

|   |      | 3.2.3                   | Read memory command via CAN                      | 28 |

|   | 3.3  | Erase memory command    |                                                  | 29 |

|   |      | 3.3.1                   | Erase memory command via USART/LINUART/UART1/2/3 | 30 |

|   |      | 3.3.2                   | Erase memory command via SPI                     | 32 |

|   |      | 3.3.3                   | Erase memory command via CAN                     | 34 |

|   | 3.4  | Write ı                 | memory command                                   | 36 |

|   |      | 3.4.1                   | Write memory command via USART/LINUART/UART1/2/3 | 37 |

|   |      | 3.4.2                   | Write memory command via SPI                     | 39 |

|   |      | 3.4.3                   | Write memory command via CAN                     | 42 |

|   | 3.5  | Speed command           |                                                  | 44 |

|   |      | 3.5.1                   | Speed command via CAN                            | 44 |

|   | 3.6  | Go co                   | mmand                                            | 46 |

|   |      | 3.6.1                   | Go command via USART/LINUART/UART1/UART2/UART3   | 46 |

|   |      | 3.6.2                   | Go command via SPI                               | 48 |

|   |      | 3.6.3                   | Go command via CAN                               | 50 |

|   | 3.7  | Sector                  | codes                                            | 51 |

UM0560 Contents

|          | 3.8          | Software model (STM8AF, STM8AL, STM8L and STM8S Series) |    |

|----------|--------------|---------------------------------------------------------|----|

| 4        | Error        | management                                              | 60 |

| 5        | Progr        | amming time                                             | 61 |

| Appendix | <b>A H</b> 0 | ow to upgrade ROP protected device                      | 62 |

|          | A.1          | Rules for upgrading ROP protected devices               | 62 |

| Appendix | в В          | ootloader entry points                                  | 63 |

| Appendix | C SI         | PI peripheral timing options                            | 65 |

|          | C.1          | SPI with busy state checking                            | 65 |

|          | C.2          | Modified erase/write RAM routines                       | 65 |

| Appendix | D P          | C software support                                      | 66 |

| Appendix | E B          | ootloader UART limitation                               | 67 |

|          | E.1          | Description                                             | 67 |

|          |              | E.1.1 UART automatic baudrate calculation               | 67 |

|          |              | E.1.2 Description of UART limitation                    | 67 |

|          | E.2          | Workaround for UART limitation                          | 68 |

| Appendix | F Li         | mitations and improvements versus bootloader versions   | 69 |

| Revision | histor       | v                                                       | 72 |

List of tables UM0560

# List of tables

| l able 1. | STM8 groups featuring a bootloader                                     | 6  |

|-----------|------------------------------------------------------------------------|----|

| Table 2.  | STM8 groups without bootloader                                         | 7  |

| Table 3.  | Bootloader versions for which bootloader activation flowchart is valid | 7  |

| Table 4.  | Initial checking                                                       | 11 |

| Table 5.  | Serial interfaces associated with STM8 devices                         | 12 |

| Table 6.  | Bootloader commands                                                    | 16 |

| Table 7.  | Bootloader codes                                                       | 16 |

| Table 8.  | Examples of delay                                                      | 39 |

| Table 9.  | STM8 sector codes                                                      | 51 |

| Table 10. | Error table                                                            | 60 |

| Table 11. | USART/LINUART/UART1/UART2/UART3 programming times                      | 61 |

| Table 12. | SPI programming time                                                   | 61 |

| Table 13. | CAN programming time                                                   | 61 |

| Table 14. | Bootloader entry points                                                | 63 |

| Table 15. | Description of limitation, improvements and added features             | 69 |

| Table 16  | Document revision history                                              | 72 |

UM0560 List of figures

# List of figures

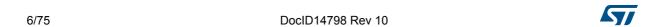

| Figure 1.  | Bootloader activation flowchart                                         | . 9 |

|------------|-------------------------------------------------------------------------|-----|

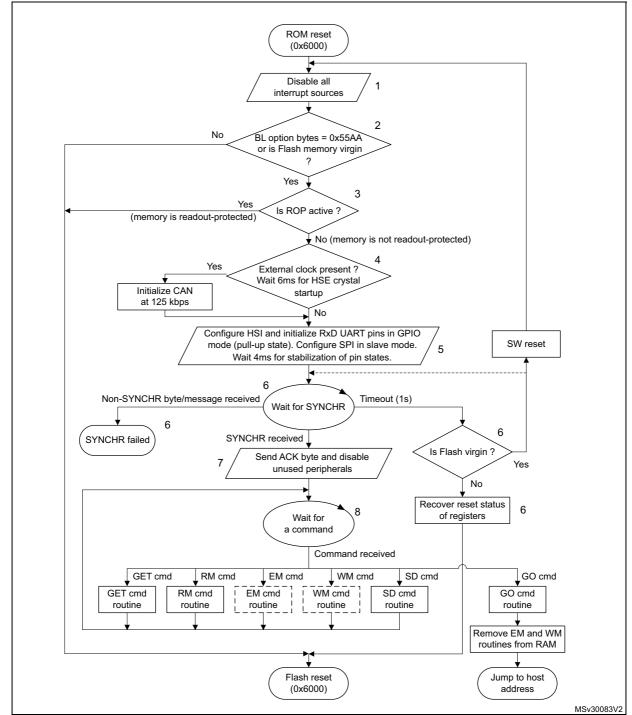

| Figure 2.  | CAN frame                                                               |     |

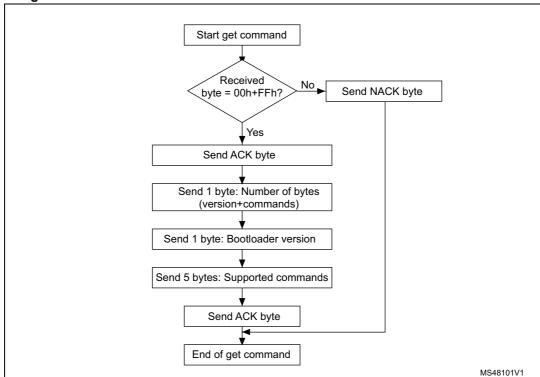

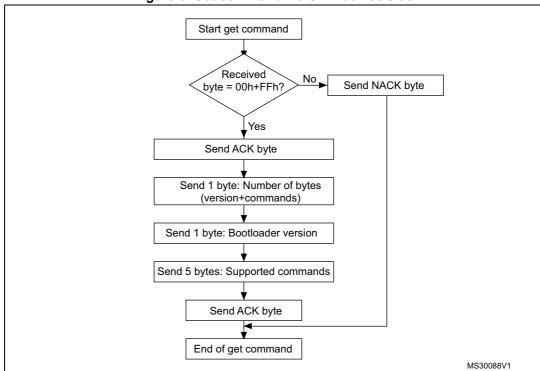

| Figure 3.  | Get command via USART/LINUART/UART1/UART2/UART3 - host side             | 17  |

| Figure 4.  | Get command via USART/LINUART/UART1/UART2/UART3 - device side           | 18  |

| Figure 5.  | Get command via SPI - host side                                         |     |

| Figure 6.  | Get command via SPI - device side                                       | 20  |

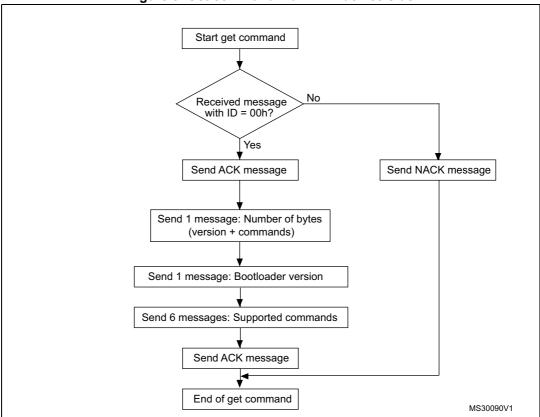

| Figure 7.  | Get command via CAN - host side                                         |     |

| Figure 8.  | Get command via CAN - device side                                       |     |

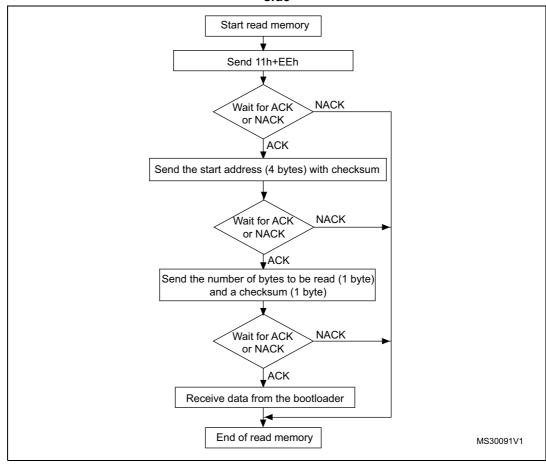

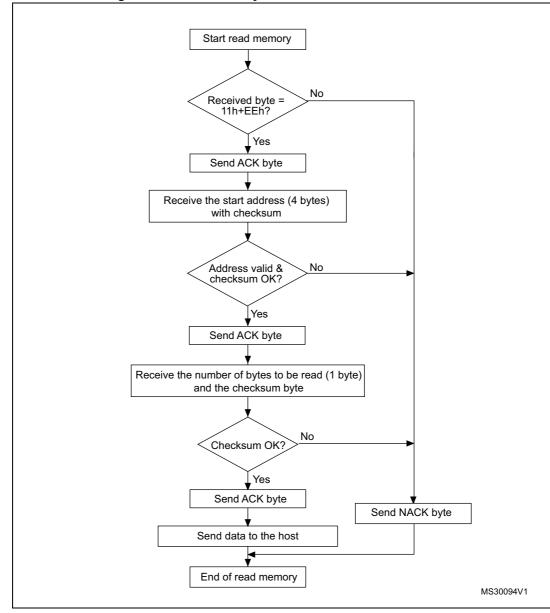

| Figure 9.  | Read memory command via USART/LINUART/UART1/UART2/UART3 - host side     | 23  |

| Figure 10. | Read memory command via USART/LINUART/UART1/UART2/UART3 - device side 2 | 24  |

| Figure 11. | Read memory command via SPI - host side                                 |     |

| Figure 12. | Read memory command via SPI - device side                               | 27  |

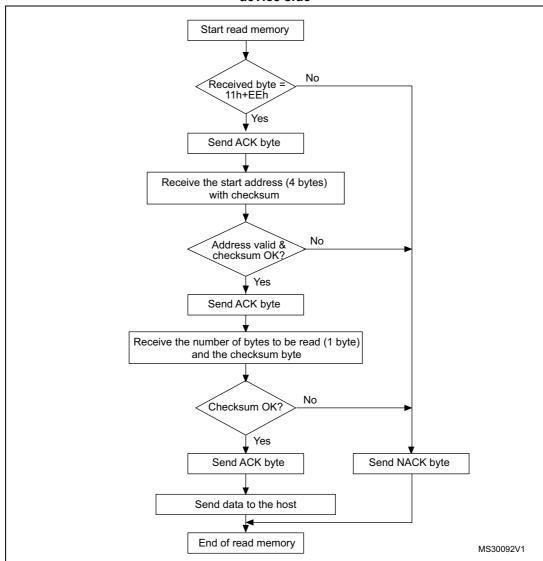

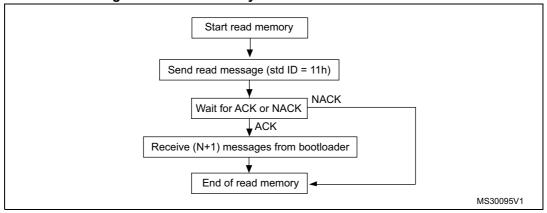

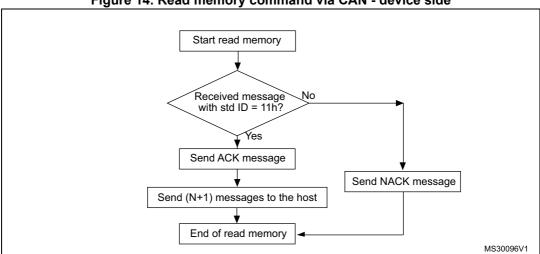

| Figure 13. | Read memory command via CAN - host side                                 | 28  |

| Figure 14. | Read memory command via CAN - device side                               |     |

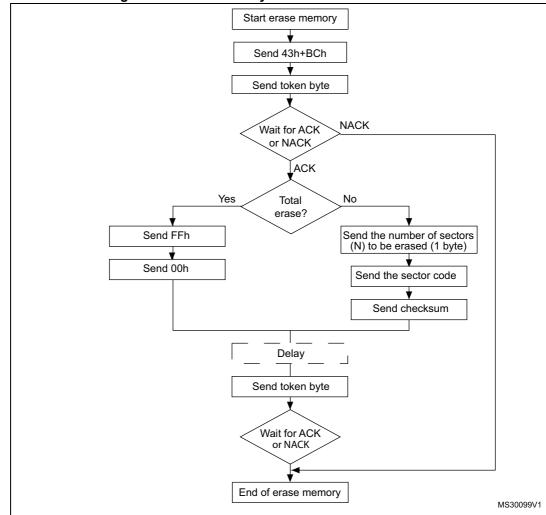

| Figure 15. | Erase memory command via USART/LINUART/UART1/2/3 - host side            | 30  |

| Figure 16. | Erase memory command via USART/LINUART/UART1/2/3 - device side          |     |

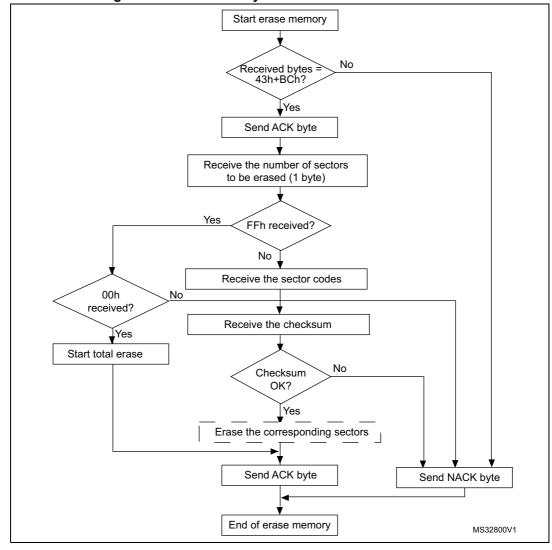

| Figure 17. | Erase memory command via SPI - host side                                | 32  |

| Figure 18. | Erase memory command via SPI - device side                              | 33  |

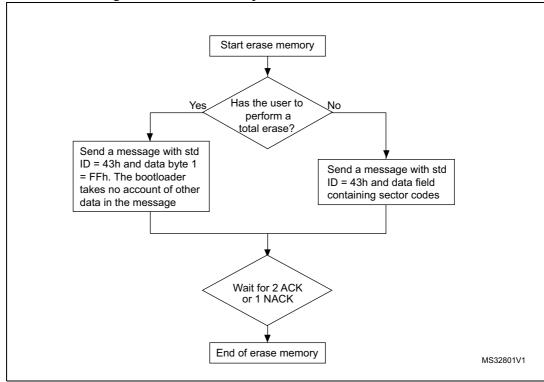

| Figure 19. | Erase memory command via CAN - host side                                |     |

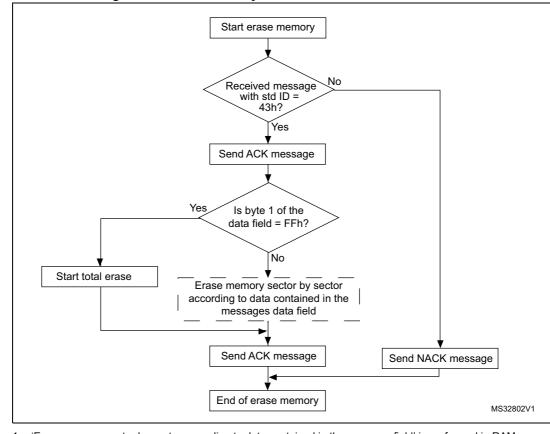

| Figure 20. | Erase memory command via CAN - device side                              |     |

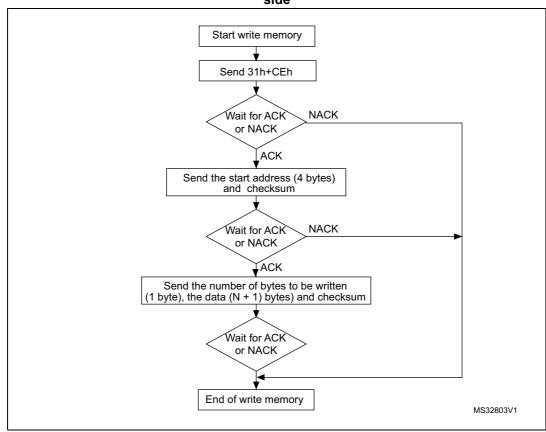

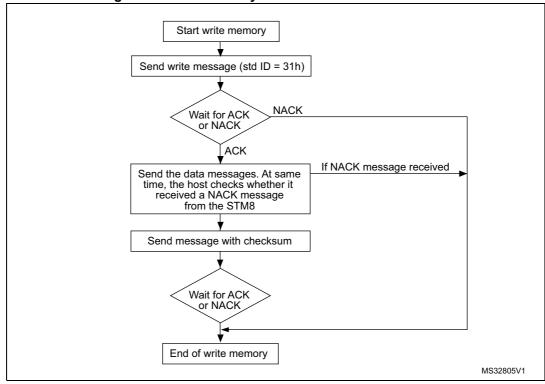

| Figure 21. | Write memory command via USART/LINUART/UART1/UART2/UART3 - host side 3  | 37  |

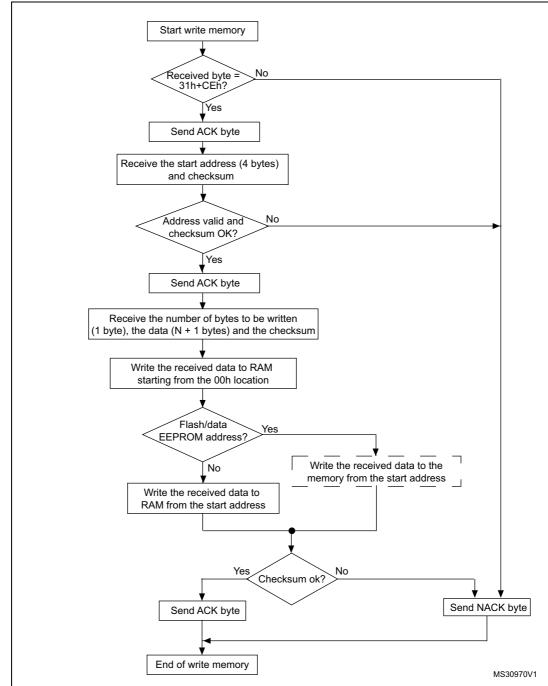

| Figure 22. | Write memory command via USART/LINUART/UART1/2/3 - device side          | 38  |

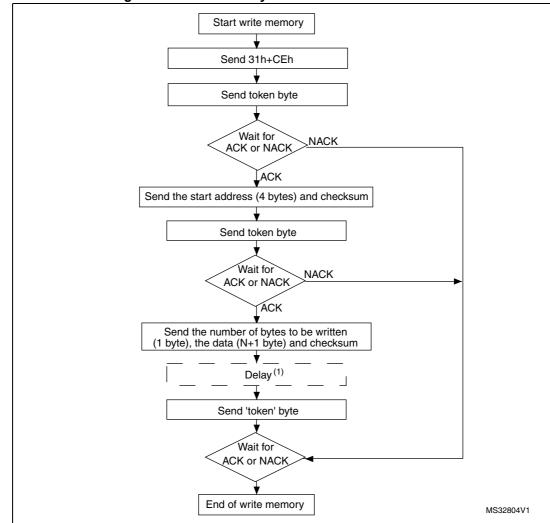

| Figure 23. | Write memory command via SPI - host side                                | 39  |

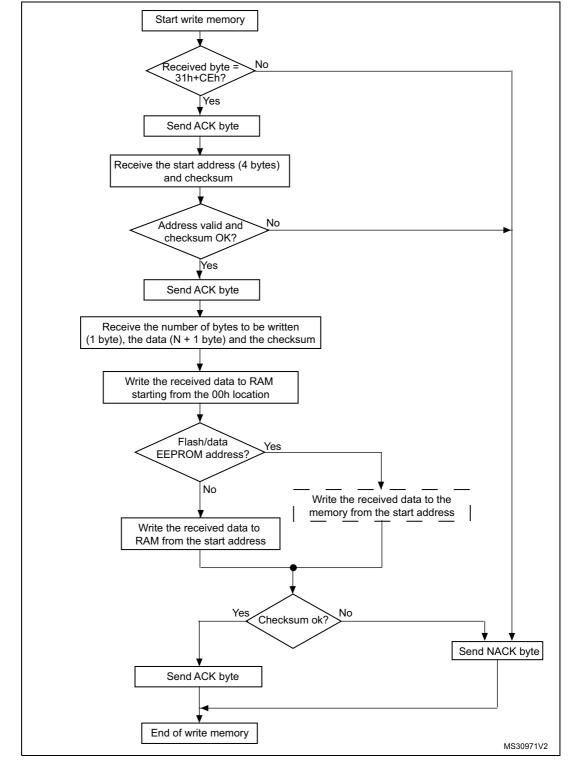

| Figure 24. | Write memory command via SPI - device side                              |     |

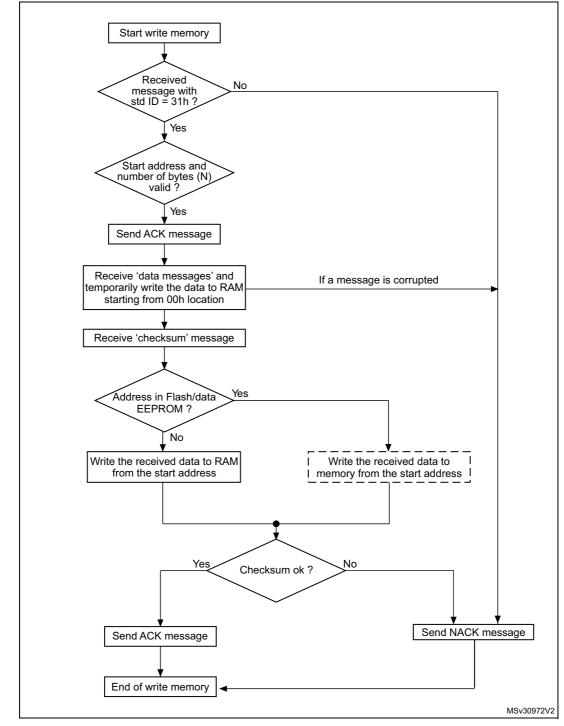

| Figure 25. | Write memory command via CAN - host side                                |     |

| Figure 26. | Write memory command via CAN - device side                              |     |

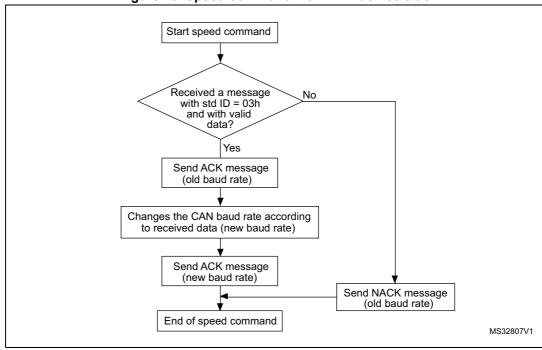

| Figure 27. | Speed command via CAN - host side                                       |     |

| Figure 28. | Speed command via CAN - device side                                     |     |

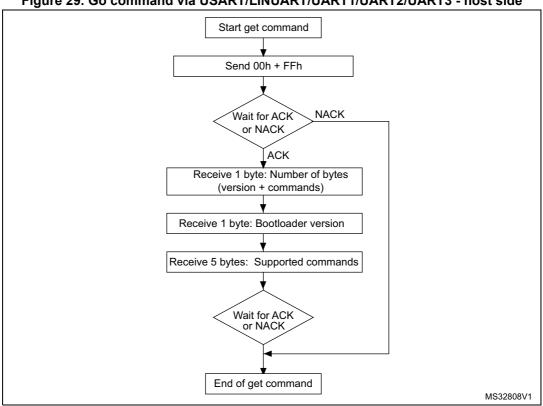

| Figure 29. | Go command via USART/LINUART/UART1/UART2/UART3 - host side              |     |

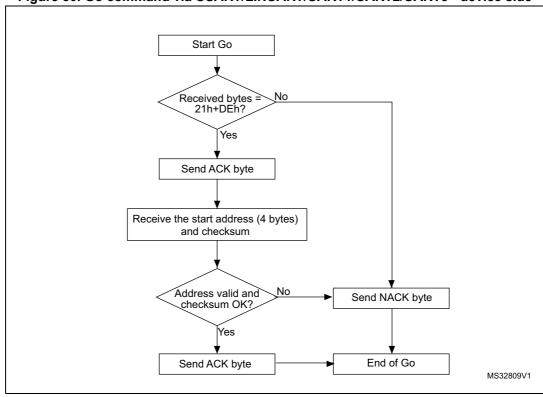

| Figure 30. | Go command via USART/LINUART/UART1/UART2/UART3 - device side            |     |

| Figure 31. | Go command via SPI - host side                                          |     |

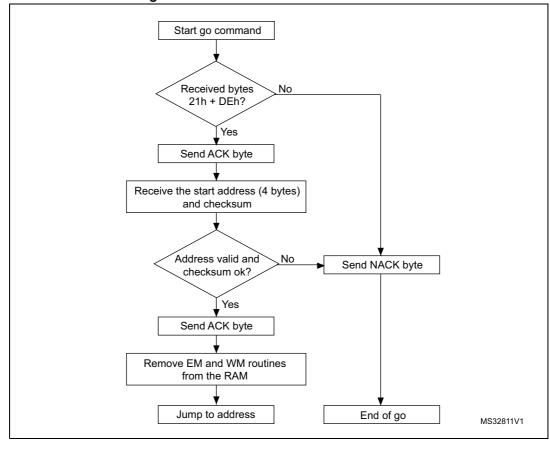

| Figure 32. | Go command via SPI - device side                                        |     |

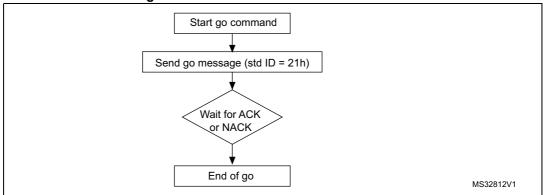

| Figure 33. | Go command via CAN - host side                                          |     |

| Figure 34. | Go command via CAN - device side                                        |     |

| Figure 35. | Delay elimination in modified RAM routines                              | ô5  |

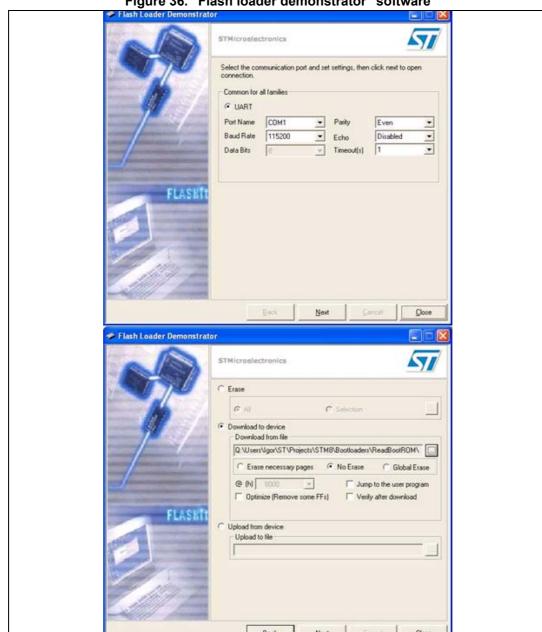

| Figure 36. | "Flash loader demonstrator" software                                    | 66  |

Bootloader introduction UM0560

#### 1 Bootloader introduction

The main task of the bootloader is to download the application program into the internal memories through the integrated peripherals (UARTs, SPI, or CAN) without using the SWIM protocol and dedicated hardware. Data are provided by any device (host) that is capable of sending information through one of the above-mentioned serial interfaces.

The bootloader permits downloading of application software into the device memories, including RAM, program and data memory, using standard serial interfaces. It is a complementary solution to programming via the SWIM debugging interface.

The bootloader code is stored in the internal boot ROM memory. After a reset, the bootloader code checks whether the program memory is virgin or whether a specific option byte is set allowing code modifications.

If these conditions are not fulfilled, the bootloader resumes and the user application is started.

In case of a successful check the bootloader is executed.

When the bootloader procedure starts, the main tasks are:

- Polling all supported serial interfaces to check which peripheral is used

- Programming code, data, option bytes and/or vector tables at the address(es) received from the host.

Each STM8 device embeds a specific bootloader code which is common to a whole group of STM8 devices. The correspondence between STM8 groups and STM8 part numbers is given in *Table 1*. These STM8 groups are used all over this user manual.

Table 1. STM8 groups featuring a bootloader

| STM8 group                                      | STM8 part numbers                                                                                                                                       |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| STM8AF and STM8S Series<br>high density         | STM8AF52xx, STM8AF6269/8x/Ax,<br>STM8AF51xx, STM8AF6169/7x/8x/9x/Ax,<br>STM8S20xxx, STM8S007xx                                                          |

| STM8AF and STM8S Series<br>medium density       | STM8AF622x/4x, STM8AF6266/68,<br>STM8AF612x/4x, STM8AF6166/68,<br>STM8S105xx, STM8S005xx                                                                |

| STM8L and STM8AL Series<br>high/medium+ density | STM8L15xx8, STM8L15xR6, STM8L16xx8,<br>STM8L052R8, STM8AL318x, STM8AL3L8x,<br>STM8AL31E8x, STM8AL3LE8x                                                  |

| STM8L and STM8AL Series<br>medium density       | STM8L15xC4, STM8L15xK4, STM8L15xG4,<br>STM8L15xC6, STM8L15xK6, STM8L15xG6,<br>STM8L052C6, STM8AL313x, STM8AL314x,<br>STM8AL316x, STM8AL3L4x, STM8AL3L6x |

| STM8L Series<br>low density                     | STM8L15xC2, STM8L15xK2, STM8L15xG2, STM8L15xC3, STM8L15xK3, STM8L15xG3, STM8Lx151F3, STM8L050J3, STM8L051F3                                             |

UM0560 Bootloader introduction

*Table 2* gives the list of STM8 devices without embedded bootloader (no ROM bootloader is implemented inside the microcontroller). When using these devices, the user has to write his own bootloader code and save it in the UBC program area (refer to STM8S, STM8AF, STM8L, STM8AL and STM8T Series reference manuals for information on the UBC area).

| STM8 group                             | STM8 part numbers                     |  |  |

|----------------------------------------|---------------------------------------|--|--|

| STM8AF and STM8S Series<br>low density | STM8AF621x/2x, STM8Sx03xx, STM8S001xx |  |  |

| STM8L101 line<br>low density           | STM8L101xx, STM8L001xx                |  |  |

| STM8T Series<br>ultra low-power        | STM8TL5xxx                            |  |  |

Table 2. STM8 groups without bootloader

#### 1.1 Bootloader activation

The STM8 hardware reset vector is located at the beginning of the boot ROM (0x00 6000), while the other interrupt vectors are in the Flash program memory starting at address 0x00 8004.

The device executes the boot ROM (jumps inside the boot ROM area) and after checking certain address locations (see *Table 4: Initial checking on page 11*), it starts to execute the bootloader or the user code defined by the reset vector (0x00 8000).

The bootloader activation flowchart is described in *Figure 1: Bootloader activation flowchart*. In previous bootloader versions, a return to the "wait for SYNCHR" state (see dashed line in *Figure 1*) was performed when the "Flash virgin" test was positive. In newer versions, it has been replaced by a software (SW) reset to prevent the customer firmware from remaining in a infinite loop (e.g. due to EMC disturbance). This bootloader modification is referred to as "EMC lockup protection" in *Table 15. Table 3* lists the bootloader versions for which the dashed line was replaced by a SW reset.

The bootloader version number of a given device is obtained by the "Get command" (see Section 3.1: Get command). The bootloader version is represented by a two-digit binary-coded decimal (BCD) number (with a decimal point between the two digits) which is coded into one byte in the "Get command" result. For example, 0x21 version byte is bootloader version 2.1.

Table 3. Bootloader versions for which bootloader activation flowchart is valid

| STM8 group                                      | Bootloader version |

|-------------------------------------------------|--------------------|

| STM8AF and STM8S Series<br>high density         | v2.2               |

| STM8AF and STM8S Series medium density          | v1.3               |

| STM8L and STM8AL Series<br>high/medium+ density | v1.0               |

Bootloader introduction UM0560

Table 3. Bootloader versions for which bootloader activation flowchart is valid

| STM8 group                             | Bootloader version |

|----------------------------------------|--------------------|

| STM8L and STM8AL Series medium density | v1.2               |

| STM8L Series<br>low density            | v1.0               |

8/75

Figure 1. Bootloader activation flowchart

- 1. See *Flowchart description on page 10* for explanation of points 1 to 8.

- 2. See Table 4: Initial checking.

- Dotted routines are loaded in RAM by the host. They are removed by the go command before jumping to the Flash program memory to execute an application.

- 4. Virgin Flash memory is tested according to the contents of address 0x8000. If [0x8000] == 0x82 or 0xAC, then the Flash memory is not virgin.

Bootloader introduction UM0560

#### Flowchart description

- Disable all interrupt sources.

- The host can start the bootloader process according to checks shown in *Table 4* (in keeping with the content of the first Flash program memory location (0x00 8000) and "bootloader enable" option bytes). The host checks the following bootloader start conditions:

- Condition 1: the host checks if the device memory is empty by inspecting the

content of address 0x00 8000 (reset vector). If the content is not equal to 0x82 or

0xAC, the device is recognized as being empty and the bootloader remains active

and waits for host commands without timeouts.

- Condition 2: the host checks if the bootloader option bytes (two bytes) are set to enable the bootloader or not. The bootloader is enabled with a value of 0x55AA and disabled by all other values (see the device datasheets for the bootloader option byte locations). If the option bytes are enabled, the bootloader remains active and waits for host commands with a 1-second timeout. If the host does not send a command within this timeout, the bootloader jumps directly to the application user vector (jump to address 0x00 8000).

- Condition 3: if the option bytes disable the bootloader (by a value different from 0x55AA), the bootloader jumps directly to the application user vector (jump to address 0x00 8000).

The above checking process is summarized in *Table 4*.

- 3. When readout protection (ROP) is active, the Flash program memory is readout protected. In this case, the bootloader stops and the user application starts. If ROP is inactive, the bootloader continues to be executed (see *Appendix A: How to upgrade ROP protected device*).

- 4. The CAN peripheral can only be used if an external clock (8 MHz, 16 MHz, or 24 MHz) is present. It is initialized at 125 Kbit/s. The UARTs and SPI peripherals do not require an external clock. There is a 6 ms waiting time for HSE crystal stabilization.

- 5. Set the high speed internal RC oscillator (HSI) to 16 MHz and initialize the UARTs receiver pins in input pull-up mode in the GPIO registers. Initialize the SPI in slave mode. Then, wait 4 ms for I/O pin voltage level stabilization. It is recommended that the host waits 10 ms from the STM8 reset before sending the SYNCHR byte/message. This is the time needed for bootloader initialization.

- 6. Interface polling: The bootloader polls all peripherals waiting for a synchronization byte/message (SYNCHR = 0x7F) within a timeout of 1 second. If a timeout occurs, either the Flash program memory is virgin in which case it waits for a synchronization byte/message in an infinite loop through a software reset, or the Flash program memory is not virgin and the bootloader restores the registers' reset status and jumps to the memory address given by the reset vector (located at 0x00 8000). For the bootloader versions listed in *Table 3*, a software reset is generated after a timeout has elapsed, in case the Flash program memory is empty (this is because it is safer to stay in an infinite loop if there is a hardware chip error).

Note: When synchronization fails (the bootloader receives a byte/message different to SYNCHR = 0x7F), two different situations can be distinguished according to the peripheral: With the UART peripherals, a device reset or power-down is necessary before synchronization can be tried again. Refer to Appendix E: Bootloader UART limitation With the CAN or SPI peripheral, the user can continue to poll the interfaces until a synchronization or a timeout occurs.

7. If the synchronization message is received by the UARTs, the bootloader automatically detects the baud rate, initializes the UART and goes to step 8 below. If the synchronization message is received by the CAN or SPI, the bootloader goes directly to step 8 below.

- Note: Once one of the available interfaces receives the synchronization message, all others are disabled.

- 8. Waiting for commands: Commands are checked in an infinite loop and executed. To exit from the bootloader, the host has to send a 'GO' command. When this is done, the bootloader removes the EM and WM routines from the RAM memory and jumps to the address selected by the host.

Note: To be able to write/erase data in Flash and EEPROM the host must write into RAM executable routines for writing and erasing. Those routines (\*.s19 files) are provided with the bootloader. Host must upload those routines at address 0xA0. See section 3.8.1: RAM erase/write routines for more information.

Actual Flash program memory status Check order **Condition checked** -> next action [0x00 8000] <> Flash program memory virgin. 1<sup>st</sup> (0x82 or 0xAC) -> continue with bootloader Flash program memory already written, 2<sup>nd</sup>  $[BL_OPT] == 0x55AA^{(1)}$ bootloader enabled by option bytes. -> continue with bootloader Device protected by ROP. 3<sup>rd</sup> ROP (readout protection) is active -> jump to Flash program memory reset vector

Table 4. Initial checking

Note: After interface initialization, the ROP bit is checked to avoid non-authorized reading of the Flash program memory and data EEPROM.

<sup>1.</sup> See device datasheet for the [BL\_OPT] location in the option byte area memory map.

Peripheral settings UM0560

## 2 Peripheral settings

This section describes the hardware settings of the STM8 communication peripherals:

- UARTs/LINUART

- SPI

- CAN

Note: During bootloading only one peripheral (first addressed) is enabled. All others are disabled.

Table 5. Serial interfaces associated with STM8 devices<sup>(1)</sup>

| STM8 groups                                     | Serial interface                                  |

|-------------------------------------------------|---------------------------------------------------|

| STM8AF Series - high density                    | USART, LINUART (in "reply" mode), CAN             |

| STM8AF Series - medium density                  | LINUART (in "reply" mode), SPI                    |

| STM8S Series - high density                     | UART1, UART3 (in "reply" mode), CAN               |

| STM8S Series - medium density                   | UART2 (in "reply" mode), SPI                      |

| STM8L Series - low density                      | UART, SPI                                         |

| STM8L and STM8AL Series - medium density        | UART                                              |

| STM8L and STM8AL Series<br>high/medium+ density | UART1, UART2, UART3 (in "reply" mode), SPI1, SPI2 |

<sup>1.</sup> The above table reflects only current bootloader versions and device states.

# 2.1 USART/UARTs settings

This peripheral supports asynchronous serial communication. The USART/UARTs settings are:

- Data frame: 1 start bit, 8 data bit, 1 parity bit set to even, 1 stop bit

- Baud rate: The baud rate is automatically detected by the bootloader. When the user sends the synchronization byte, 0x7F, the bootloader automatically detects the baud rate and sets the USART/UARTs to the same baud rate. Maximum baud rate = 1 Mbps (115200 baud for STM8L/AL-high/medium+ density); minimum baud rate = 4800 bps.

To perform automatic speed detection, the RxD line must be stable in the application board (internal pull-up is enabled on the RxD line by the bootloader).

#### Pin settings:

- While bootloader is waiting for synchronization byte (SYNCH = 0x7F), RxD pins are set to input mode with pull-up.

- If bootloader is activated by USART/UART then TxD pins are set to push-pull mode.

- If bootloader is not activated (no SYNCH byte received within 1 second timeout) then all USART/UART pins are set to default reset state.

- If bootloader is activated by another interface (except USART/UART) then RxD pins remain in input mode with pull-up.

UM0560 Peripheral settings

#### 2.1.1 LINUART/UARTs in "reply" mode settings

Settings are:

- Data frame: 1 start bit, 8 data bit, no parity bit, 1 stop bit

- Baud rate: The baud rate is automatically detected by the bootloader. When the user sends the synchronization byte 0x7F, the bootloader automatically detects the baud rate and sets the UARTs to the same baud rate. Maximum baud rate = 550 kbps(115200 baud for STM8L/AL-high/medium+ density); minimum baud rate = 4800 bps.

To perform automatic speed detection, the RxD line must be stable in the application board (internal pull-up is enabled on the RxD line by the bootloader).

#### Reply mode

The host must reply to all the bytes sent from the bootloader. If TxD and RxD lines share the same physical medium (for example, 1-wire communication), then host replies are not necessary since RxD and TxD pins coincide.

Pin settings:

- While bootloader is waiting for synchronization byte (SYNCH = 0x7F), RxD pins are set to input mode with pull-up.

- If bootloader is activated by LINUART/UART then TxD pins are set to push-pull mode.

- If bootloader is not activated (no SYNCH byte received within 1 second timeout) then all LINUART/UART pins are set to default reset state.

- If bootloader is activated by another interface (except LINUART/UART) then RxD pins remain in input mode with pull-up.

## 2.2 SPI settings

The SPI settings are:

- 8 data bit, MSB first

- Bit rate: Set by the host which acts as a master

- Peripheral set in slave mode with software management of NSS

- Data polarity: CPOL = 0 (SCK to 0 when idle), CPHA = 0 (the first clock transition is the first data capture edge).

Before sending a 'token' byte, the host has to wait for a delay of a specified period of time. If this period is not quantified, it is equal to 6 µs.

The SPI peripheral is accessible via SPI\_SCK, SPI\_MOSI and SPI\_MISO pins, with the following settings:

- While bootloader is waiting for synchronization byte (SYNCH = 0x7F) SPI\_MISO pins are set to push-pull mode.

- If bootloader is not activated (no SYNCH byte received within 1 second timeout) then all SPI\_MISO pins are set to default reset state.

- If bootloader is activated by another interface (except SPI) then SPI\_MISO pins remain in push-pull mode.

Peripheral settings UM0560

## 2.3 CAN settings

To address additional devices on the same bus, the CAN protocol provides a standard identifier field (11-bit) and an optional extended identifier field (18-bit) in the frame.

Figure 2 shows the CAN frame that uses the standard identifier only.

Figure 2. CAN frame

The CAN settings are as follows:

- Standard identifier (not extended)

- Bit rate

By default, it is 125 Kbit/s. The runtime can be changed via the speed command to achieve a maximum bit rate of 1 Mbit/s.

The transmit settings (from the STM8 to the host) are:

- Tx mailbox0: On

- Tx mailbox1 and Tx mailbox2: Off

- Tx identifier: 0x02

- Outgoing messages contain 1 data byte

The receive settings (from the host to the STM8) are:

- The synchronization byte, 0x7F, is in the RX identifier and not in the data field.

- The RX identifier depends on the command (0x00, 0x03, 0x11, 0x21, 0x31, 0x43).

- Error checking: If the error field (bit [6:4] in the CESR register) is different from 000b, the message is discarded and a NACK is sent to the host.

- In FIFO overrun condition, the message is discarded and a NACK is sent to the host.

Incoming messages can contain from 1 to 8 data bytes.

UM0560 Peripheral settings

The CAN peripheral is accessible via CAN\_TX and CAN\_RX pins, with the following settings:

- While bootloader is waiting for synchronization byte (SYNCH = 0x7F), CAN\_TX pin is set to push-pull mode.

- If bootloader is not activated (no SYNCH byte received within 1 second timeout) then CAN\_TX pin is set to default reset state.

- If bootloader is activated by another interface (except CAN) then CAN\_TX pin remains in push-pull mode.

#### 3 Bootloader command set

The commands supported by the bootloader are listed in *Table 6* below.

**Table 6. Bootloader commands**

| Command      | Command code | Command description                                                                                                  |

|--------------|--------------|----------------------------------------------------------------------------------------------------------------------|

| Get          | 0x00         | Gets the version and the allowed commands supported by the current version of the bootloader                         |

| Read memory  | 0x11         | Reads up to 256 bytes of memory starting from an address specified by the host                                       |

| Erase memory | 0x43         | Erases from one to all of the Flash program memory/data EEPROM sectors                                               |

| Write memory | 0x31         | Writes up to 128 bytes to RAM or the Flash program memory/data EEPROM starting from an address specified by the host |

| Speed        | 0x03         | Allows the baud rate for CAN runtime to be changed                                                                   |

| Go           | 0x21         | Jumps to an address specified by the host to execute a loaded code                                                   |

Table 7. Bootloader codes

| Name  | Code | Description                                                                                                                                                                                                                                       |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYNCH | 0x7F | Synchronization byte                                                                                                                                                                                                                              |

| ACK   | 0x79 | Acknowledge                                                                                                                                                                                                                                       |

| NACK  | 0x1F | No acknowledge                                                                                                                                                                                                                                    |

| Token | 0xXX | Any byte which the host sends to the bootloader via the SPI interface to receive an answer from the bootloader (it is necessary to put data into the SPI when it is needed to receive data - SPI clock generation) The usual token value is 0x00. |

| BUSY  | 0xAA | Busy flag status                                                                                                                                                                                                                                  |

When the bootloader receives a command via the UARTs, CAN or SPI peripherals, the general protocol is as follows:

- 1. The bootloader sends an ACK byte (0x79) to the host and waits for an address and for a checksum byte, both of which are checked when received.

- 2. When the address is valid and the checksum is correct, the bootloader transmits an ACK byte (0x79), otherwise it transmits a NACK byte (0x1F) and aborts the command. The bootloader waits for the number of bytes to be transmitted (N bytes) and for its complemented byte (checksum).

- If the checksum is correct, it carries out the command, starting from the received address.

- If the checksum is incorrect, a NACK (0x1F) byte is sent before aborting the command.

The bootloader protocols via the UARTs, and SPI are identical on the device side, but differ regarding the host. A token byte is needed when sending each byte to the host via SPI (see *Figure 5, Figure 11, Figure 23*, and *Figure 31*).

The bootloader protocol via CAN differs from all other peripherals.

#### 3.1 **Get command**

The get command allows the host to get the version of the bootloader and the supported commands. When the bootloader receives the get command, it transmits the bootloader version and the supported command codes to the host.

#### 3.1.1 Get command via USART/LINUART/UART1/ UART2/UART3

Figure 3. Get command via USART/LINUART/UART1/UART2/UART3 - host side Start get command Send 00h + FFh **NACK** Wait for ACK or NACK ACK Receive 1 byte: Number of bytes (version + commands) Receive 1 byte: Bootloader version Receive 5 bytes: Supported commands Wait for ACK or NACK End of get command MS48100V1

#### The host sends the bytes as follows

Byte 1: - Command ID 0x00 Byte 2: - Complement 0xFF

Figure 4. Get command via USART/LINUART/UART1/UART2/UART3 - device side

#### The STM8 sends the bytes as follows

Byte 1: ACK (after the host has sent the command)

Byte 2: N = 5 = the number of bytes to be sent -1 (1 <= N +1 <= 256)

Byte 3: Bootloader version (0 < version <= 255)

Byte 4: 0x00 - Get command

Byte 5: 0x11 - Read memory command

Byte 6: 0x21 - Go command

Byte 7: 0x31 - Write memory command

Byte 8: 0x43 - Erase memory command

Byte 9: ACK

18/75

#### 3.1.2 Get command via SPI

Start get command Send 00h + FFh Send token byte Wait for ACK or NACK ACK Send token byte Receive 1 byte (05h): Number of bytes Send token byte Receive 1 byte: Bootloader version Send token byte Receive 1 byte (00h): Get command ID Send token byte Receive 1 byte (11h): Read command ID Send token byte Receive 1 byte (21h): Go command ID Send token byte Receive 1 byte (31h): Write command ID Send token byte Receive 1 byte (43h): Erase command ID Send token byte Wait for ACK End of get command or NACK MS30087V1

Figure 5. Get command via SPI - host side

#### The host sends the bytes as follows

Byte 1: 0x00 - Command ID

Byte 2: 0xFF - Complement

Byte 3 (token): 0xXY; host waits for ACK or NACK

Byte 4 (token): 0xXY; host waits for 0x05

• • •

Byte 11 (token): 0x XY; host waits for ACK or NACK.

Figure 6. Get command via SPI - device side

#### The STM8 sends the bytes as follows

Byte 1: ACK

Byte 2: N = 5 = the number of bytes to be sent -1 (1 <= N +1 <= 256)

Byte 3: Bootloader version (0 < version <= 255)

Byte 4: 0x00 - Get command

Byte 5: 0x11 - Read memory command

Byte 6: 0x21 - Go command

Byte 7: 0x31 - Write memory command

Byte 8: 0x43 - Erase memory command

Byte 9: ACK

#### 3.1.3 Get command via CAN

Start get command Send message with std ID = 00h Wait for ACK NACK or NACK ∐ACK Receive 1 message: number of bytes (version + commands) Receive 1 message: Bootloader version Receive 1 message: Get command Receive 1 message: Speed command Receive 1 message: Read command Receive 1 message: Go command Receive 1 message: Write command Receive 1 message: Erase command Wait for ACK or NACK End of get command MS30089V1

Figure 7. Get command via CAN - host side

#### The host sends the messages as follows

Command message: Std ID = 0x00, data length code (DLC) = 'not important'.

Figure 8. Get command via CAN - device side

#### The STM8 sends the messages as follows

Message 1: Std ID = 0x02, DLC = 1, data = ACK

Message 2: Std ID = 0x02, DLC = 1 data = N = 6 = the number of bytes to be sent -1

$(1 \le N + 1 \le 256)$

Message 3: Std ID = 0x02, DLC = 1, data = bootloader version (0 < version <= 255)

Message 4: Std ID = 0x02, DLC = 1, data = 0x00

- Get command

Message 5: Std ID = 0x02, DLC = 1, data = 0x03

- Speed command

Message 6: Std ID = 0x02, DLC = 1, data = 0x11

- Read memory command

Message 7: Std ID= 0x02, DLC = 1, data = 0x21

- Go command

Message 8: Std ID = 0x02, DLC = 1, data = 0x31

- Write memory command

Message 9: Std ID= 0x02, DLC = 1, data = 0x43

- Erase memory command

Message 10: Std ID = 0x02, DLC = 1, data = ACK

#### 3.2 Read memory command

The read memory command reads the memory (RAM, Flash program memory/data EEPROM or registers). When the bootloader receives the read memory command, it transmits the needed data ((N + 1) bytes) to the host, starting from the received address.

#### 3.2.1 Read memory command via USART/LINUART/UART1/2/3

Figure 9. Read memory command via USART/LINUART/UART1/UART2/UART3 - host side

The valid addresses are RAM, Flash program memory/data EEPROM, and register addresses (see product datasheets).

If the bootloader receives an invalid address, an error occurs (see Table 10: Error table on page 60).

#### The host sends the bytes to the STM8 as follows

Bytes 1-2: 0x11+0xEE

Bytes 3-6: The start address (32-bit address)

Byte 3 = MSB Byte 6 = LSB

Byte 7: Checksum = XOR (byte 3, byte 4, byte 5, byte 6)

Byte 8: The number of bytes to be read -1 (0  $\leq$  N  $\leq$  255)

Byte 9: Checksum (complement of byte 8)

Figure 10. Read memory command via USART/LINUART/UART1/UART2/UART3 - device side

#### 3.2.2 Read memory command via SPI

Figure 11. Read memory command via SPI - host side

Valid addresses are RAM, Flash program memory/data EEPROM, and register addresses (see product datasheets). If the bootloader receives an invalid address, an error occurs (see *Table 10 on page 60*).

#### The host sends the bytes to the STM8 as follows

Byte 1: 0x11 - Command ID

Byte 2: 0xEE - Complement

Byte 3 (token): 0xXY; host waits for ACK or NACK

Bytes 4 to 7: The start address (32-bit address)

Byte 4 = MSBByte 7 = LSB

Byte 8: Checksum = XOR (byte 4, byte 5, byte 6, byte 7)

Byte 9 (token): 0xXY; host waits for ACK or NACK

Byte 10: The number of bytes to be read -1 (0  $\leq$  N  $\leq$  255)

Byte 11: Checksum (complement of byte 10)

Byte 12 (token): 0xXY; host waits for the 1<sup>st</sup> data byte

Byte 12+N (token): 0xXY; host waits for the N+1<sup>th</sup> data byte

Figure 12. Read memory command via SPI - device side

#### 3.2.3 Read memory command via CAN

The CAN message sent by the host is as follows:

- The ID contains the command type (0x11)

- The data field contains a destination address (4 bytes, byte 1 is the MSB and byte 4 is LSB of the address) and the 'number of bytes' (N) to be read.

Figure 13. Read memory command via CAN - host side

Valid addresses are RAM, Flash program memory/data EEPROM, and register addresses (see product datasheets). If the bootloader receives an invalid address, an error occurs (see Table 10 on page 60).

#### The host sends the command messages as follows

Std ID = 0x11, DLC = 0x05, data = MSB, 0xXX, 0xYY, LSB, N (where  $0 < N \le 255$ ).

Figure 14. Read memory command via CAN - device side

577

#### The STM8 sends the messages as follows

ACK message: Std ID = 0x02, DLC = 1, data = ACK

Data message 1: Std ID = 0x02, DLC = 1, data = 0xXX

Data message 2: Std ID = 0x02, DLC = 1, data = 0xXX

. . .

Data message (N+1): Std ID = 0x02, DLC = 1, data = 0xXX

Note: The bootloader sends as many data messages as bytes which can be read.

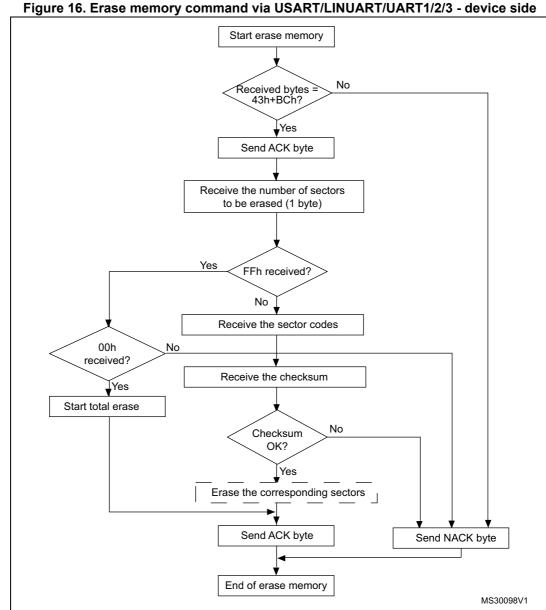

#### 3.3 Erase memory command

The erase memory command allows the host to erase sectors of the Flash program memory/data EEPROM.

The bootloader receives the erase command message, when the ID contains the command type (0x43) and the data field contains the sectors to be erased (see *Table 9: STM8 sector codes on page 51*). A sector size is 1 Kbyte, therefore, the granularity with the erase command is eight blocks (1 block = 128 bytes). If the host wants to erase one byte only, the write command (write 0x00) can be used.

#### Erase memory command description

- The bootloader receives one byte which contains the number (N) of sectors to be erased. N is device-dependent.

- 2. Then, the bootloader receives (N + 1) bytes, where each byte contains a sector code (see *Table 9: STM8 sector codes on page 51*).

#### 3.3.1 Erase memory command via USART/LINUART/UART1/2/3

Start erase memory Send 43h+BCh NACK Wait for ACK or NACK ACK Yes No Total erase? Send FFh Send the number of sectors to be erased (1 byte) Send 00h Send the sector codes Send checksum Wait for ACK or NACK End of erase memory

Figure 15. Erase memory command via USART/LINUART/UART1/2/3 - host side

- "Total erase" erases program and data EEPROM. The bootloader erases the memory sector by sector.

- A sector is 1 Kbyte for all devices. Therefore, the granularity of the erase command is 8 blocks. To erase one byte, the write command can be used by writing 0x00.

Warning: If the host sends an erase command that includes correct sector code and one or more forbidden sector codes (see Table 9: STM8 sector codes), the command fails.

#### The host sends the bytes as follows

Byte 1: 0x43 - Command ID Byte 2: 0xBC - Complement

Byte 3: 0xFF or number of sectors to be erased  $(0 \le N \le M)$ ; if N > M, a cmd\_error occurs in the bootloader, after which the bootloader receives N + 1 data bytes and the checksum (i.e. the host completes the command).

N is product-dependent. Note:

M = (size of the Flash program memory in Kbyte) + (size of data EEPROM in Kbyte) -1. Example STM8S Series-high density:

30/75 DocID14798 Rev 10

MS30097V1

M = 129, because Flash program memory is 128 Kbytes and data EEPROM is 2 Kbytes (128 + 2 -1).

Example STM8S Series-medium density:

M = 32, because Flash program memory is 32 Kbytes and data EEPROM is 1 Kbyte (32 + 1 - 1).

Byte 4 or N+1 bytes: 0x00 or (N+1 bytes and then checksum: XOR(N,[N+1 data bytes])). Example STM8L and STM8AL Series-low density:

M = 8, because Flash program memory is 8 Kbytes and data EEPROM (256 bytes) is in next starting 1 Kbyte (8 + 1 - 1).

Byte 4 or N+1 bytes: 0x00 or (N+1 bytes and then checksum: XOR(N,[N+1 data bytes])).

'Erase the corresponding sectors' routine is performed in RAM. The user therefore has to download the erase routine in RAM before sending an erase command. Note that for some bootloader versions this is not necessary (see 3.8.1: RAM erase/write routines).

#### 3.3.2 Erase memory command via SPI

Figure 17. Erase memory command via SPI - host side

When using the erase command via SPI, it is necessary to wait for a brief time interval (see 'delay' in Figure 17 above) before sending the last token byte. This delay interval depends on the number of sectors (N) to be erased. Delay = 30 \* (N + 1)[ms], where 0 <= N <= 32. N = 32 in the case of total erase. See also Appendix C: SPI peripheral timing options.</li>

#### The host sends the bytes as follows

Byte 1: 0x43 - Command ID

Byte 2: 0xBC - Complement

Byte 3 (token): 0xXY; host waits for ACK or NACK

Byte 4: 0xFF or number of sectors to be erased  $(0 \le N \le 32)$

If N > 32 a 'cmd\_error' occurs.

Byte 5 or N+1 bytes: 0x00 or (N+1 bytes and then checksum:

XOR(N,[N+1 data bytes])

Last byte (token): 0xXY; host waits for ACK or NACK.

DocID14798 Rev 10

Figure 18. Erase memory command via SPI - device side

<sup>&#</sup>x27;Erase the corresponding sectors' routine is performed in RAM. The user therefore has to download the erase routine in RAM before sending an erase command. Note that for some bootloader versions this is not necessary (see 3.8.1: RAM erase/write routines).

#### 3.3.3 Erase memory command via CAN

Figure 19. Erase memory command via CAN - host side

- 1. The bootloader erases the memory sector by sector.

- A sector is 1 Kbyte for all devices. Therefore, the granularity of the erase command 8 blocks. To erase one byte, the write command can be used by writing 0x00.

Warning: If the host sends an erase command that includes some correct sector code and one or more forbidden sector codes (see *Table 9: STM8 sector codes*), the command fails and no

block is erased.

#### The host sends the message as follows

Total erase message: Std ID = 0x43, DLC = 0x01, data = 0xFF.

Erase sector by sector message: Std ID = 0x43, DLC = 0x01 to 0x08, data = see *Table 9: STM8 sector codes*.

Figure 20. Erase memory command via CAN - device side

'Erase memory sector by sector according to data contained in the message field' is performed in RAM.

The user therefore has to download the erase routine in RAM before sending an erase command. Note

that for some bootloader versions this is not necessary (see 3.8.1: RAM erase/write routines).

## 3.4 Write memory command

The write memory command allows the host to write data into any memory address (RAM, Flash program memory/data EEPROM or registers) starting from the received address. Incoming data are always written in RAM before being loaded in the memory locations decided by the host. The bootloader then checks whether the host wants to write in RAM or in the Flash program memory/data EEPROM.

The maximum length of the block to be written for the STM8 is 128 data bytes. To write the data in the Flash program memory/data EEPROM locations, the bootloader performs two different write operations:

- 1. WordWrite/FastWordWrite: Writes a byte in the Flash program memory/data EEPROM. It is used when the number of bytes (N) sent from the host is less than 128. In this case the bootloader performs the operation N times.

- 2. BlockWrite: Writes a block in the Flash program memory/data EEPROM. It is used when the number of bytes (N) sent from the host is 128 and the destination address is an integer module of 128. In other words, to use this operation, the block sent from the host has to be aligned with a memory block. If not aligned, the byte write operation is used (which is slower).

### 3.4.1 Write memory command via USART/LINUART/UART1/2/3

Figure 21. Write memory command via USART/LINUART/UART1/UART2/UART3 - host side

See product datasheets for valid addresses. If the start address is invalid, an add\_error occurs (see Table 10: Error table on page 60).

### The host sends the bytes as follows

Byte 1: 0x31 - Command ID

Byte 2: 0xCE - Complement

Bytes 3-6: The start address (32-bit address)

Byte 3 = MSB Byte 6 = LSB

Byte 7: Checksum = XOR (byte 3, byte 4, byte 5, byte 6)

Byte 8: The number of bytes to be received -1: N = 0 ... 127

If N > 127, a cmd\_error occurs in the bootloader.

N+1 bytes: Max 128 data bytes

Checksum byte: XOR (N,[N+1 data bytes]).

Figure 22. Write memory command via USART/LINUART/UART1/2/3 - device side

<sup>&#</sup>x27;Write the received data to RAM from the start address' is performed in RAM. The user therefore has to download the write routine in RAM before sending a write command. Note that for some bootloader versions this is not necessary (see 3.8.1: RAM erase/write routines).

### 3.4.2 Write memory command via SPI

Figure 23. Write memory command via SPI - host side

1. Delay or poll "BUSY" flag if device supports it.

The delay is calculated according to Equation 1.

### **Equation 1**

Delay =  $8.45 \times n[ms]$

Where 'n' is the number of write cycles (number of bytes or number of blocks - see Table 8).

Table 8. Examples of delay

| Write command                             | Delay (ms) |

|-------------------------------------------|------------|

| 128 bytes aligned with a memory block     | 8.45       |

| 128 bytes not aligned with a memory block | 1082       |

| 1 byte                                    | 8.45       |

| 10 bytes                                  | 84.5       |

In SPI mode, if the device supports sending a "BUSY" flag during Flash/EEPROM memory programming, the delay can be replaced by polling the device status (a set of token bytes are sent to the device). During programming the device sends the BUSY flag (0xAA) through SPI. When the programming is finished, the device sends an ACK/NACK answer to indicate if the programming was correct or has failed.

Currently, such polling is allowed only for STM8AF/S-medium density devices with modified RAM routines (see *Appendix C: SPI peripheral timing options*). On STM8L/AL-low density and STM8L/AL-high/medium+ density devices, the BUSY flag is sent through the SPI interface.

### The host sends the bytes as follows

Byte 1: 0x31 - Command ID

Byte 2: 0xCE - Complement

Byte 3 (token): XY; host waits for ACK or NACK Bytes 4 to 7: The start address (32-bit address)

> Byte 4 = MSBByte 7 = LSB

Byte 8: Checksum = XOR (byte 4, byte 5, byte 6, and byte 7)

Byte 9 (token): XY; host waits for ACK or NACK

Byte 10: The number of data bytes to be received -1:  $N = 0 \dots 127$ );

If N > 127, a cmd\_error occurs in the bootloader.

N+1 bytes: Max 128 data bytes

Checksum byte: XOR (N,[N+1 data bytes])

**Important:** before sending the token byte, the host must wait for the bootloader to finish writing all data into the memory. See previous delay

(or polling) description.

Last byte (token): 0xXY; host waits for ACK or NACK

Figure 24. Write memory command via SPI - device side

<sup>&#</sup>x27;Write the received data to RAM from the start address' is performed in RAM. The user therefore has to download the write routine in RAM before sending a write command. Note that for some bootloader versions this is not necessary (see 3.8.1: RAM erase/write routines).

### 3.4.3 Write memory command via CAN

Figure 25. Write memory command via CAN - host side

See product datasheets for valid addresses. If the bootloader receives an invalid address, an add\_error occurs (see Table 10: Error table on page 60).

#### The host sends the messages as follows

Command message: Std ID = 0x31, DLC = 0x05, data = MSB, 0xXX, 0xYY, LSB, N. N =  $0 \dots 127$ , number of data bytes -1. If N > 127, a cmd error occurs in the bootloader.

Data message\_1: Std ID = 0x04, DLC\_1 = 1 to 8, data = byte\_11, ... byte\_18

Data message\_2: Std ID = 0x04, DLC\_2 = 1 to 8, data = byte\_21, ... byte\_28

Data message\_3: Std ID = 0x04, DLC\_3 = 1 to 8, data = byte\_31, ... byte\_38

Data message\_M: Std ID = 0x04, DLC\_M = 1 to 8, data = byte\_m1, ..., byte\_M8

Checksum message: Std ID = 0x04, DLC = 1, data = XOR (N,[N+1 data bytes])

Note: 1. DLC\_1 + DLC\_2 + ... DLC\_M = 128 maximum

2. The bootloader does not check the standard ID of the data and checksum messages. Therefore, an ID from 0x00 to 0xFF can be used. It is recommended to use 0x04.

Figure 26. Write memory command via CAN - device side

<sup>1.</sup> Write the received data to the Flash program memory/data EEPROM from the start address' is performed in RAM. The user therefore has to download the write routine in RAM before sending a write command. Note that for some bootloader versions this is not necessary (see 3.8.1: RAM erase/write routines).

#### **Speed command** 3.5

The speed command allows the baud rate for CAN runtime to be changed. It can be used only if the CAN is the peripheral being used.

#### 3.5.1 Speed command via CAN

Start speed command Received a message No with std ID = 03h and with valid data? Send ACK message (old baud rate) Changes the CAN baud rate according to received data (new baud rate) Send ACK message (new baud rate) Send NACK message (old baud rate) End of speed command MS32806V1

Figure 27. Speed command via CAN - host side

After setting the new baud rate, the bootloader sends the ACK message. Therefore, the host sets its baud rate while waiting for the ACK.

### The host sends the message as follows

Command message: Std ID = 0x03, DLC = 0x01, data = 0xXX where 0xXX assumes the following values depending on the baud rate to be set with HSE:

- 0x01 -> baud rate = 125 kbps

- $0x02 \rightarrow baud rate = 250 kbps$

- $0x03 \rightarrow baud rate = 500 kbps$

- 0x04 -> baud rate = 1 Mkbps

Figure 28. Speed command via CAN - device side

### 3.6 Go command

The go command executes the downloaded code, or any other code, by branching to an address specified by the host.

Note:

After the Go command has executed, the program and data memories are in an unlocked state. Applications should lock program and data memories to set the default memory protection state.

### 3.6.1 Go command via USART/LINUART/UART1/UART2/UART3

Figure 29. Go command via USART/LINUART/UART1/UART2/UART3 - host side

The valid addresses are RAM, Flash program memory/data EEPROM, and register addresses (see product datasheets). If the bootloader receives an invalid address, an 'add error' occurs (see *Table 10: Error table on page 60*).

### The host sends the bytes as follows

Byte 1: 0x21 - Command ID

Byte 2: 0xDE - Complement

Bytes 3-6: The start address (32-bit address)

Byte 3 = MSBByte 6 = LSB

Byte 7: Checksum = XOR (byte 3, byte 4, byte 5, byte 6).

577

Figure 30. Go command via USART/LINUART/UART1/UART2/UART3 - device side

#### 3.6.2 Go command via SPI

Start Go Send 21h+DEh Send token byte NACK Wait for ACK or NACK ACK Send the start address (4 bytes) and checksum Send token byte Wait for ACK or NACK

Figure 31. Go command via SPI - host side

End of Go

### The host sends the bytes as follows

Byte 1: 0x21 - Command ID Byte 2: 0xDE - Complement Byte 3 (token): 0xXY; host waits for ACK or NACK Bytes 4 to 7: The start address (32-bit address)

> Byte 4 = MSB Byte 7 = LSB

48/75

Byte 8: Checksum = XOR (byte 4, byte 5, byte 6, and byte 7)

Byte 9 (token): 0xXY; host waits for ACK or NACK.

DocID14798 Rev 10

MS32810V1

The valid addresses are RAM, Flash program memory/data EEPROM and register addresses (see product datasheets). If the bootloader receives an invalid address, an 'add error' occurs (see *Table 10: Error table* on page 60).

Figure 32. Go command via SPI - device side

### 3.6.3 Go command via CAN

Figure 33. Go command via CAN - host side

1. See product datasheets for valid addresses.

### The host sends the bytes as follows

Go command message: Std ID =0x21, DLC = 0x04, data = MSB, 0xXX, 0xYY, LSB

Start go command

Received message with std ID = 21h and with a valid address?

Yes

Send ACK message

Jump to address

End of go

MS32813V1

Figure 34. Go command via CAN - device side

57

# 3.7 Sector codes

Table 9. STM8 sector codes

|                | Flash program memory/data EEPROM           |                                              |                                              |                                                        |                             |  |

|----------------|--------------------------------------------|----------------------------------------------|----------------------------------------------|--------------------------------------------------------|-----------------------------|--|

| Sector<br>code | STM8AF and<br>STM8S Series<br>high density | STM8AF and<br>STM8S Series<br>medium density | STM8L and<br>STM8AL Series<br>medium density | STM8L and<br>STM8AL Series<br>high/medium<br>+ density | STM8L Series<br>low density |  |

| 0x00           | 0x00 8000 -><br>0x00 83FF                  | 0x00 8000 -><br>0x00 83FF                    | 0x00 8000 -><br>0x00 83FF                    | 0x00 8000 -><br>0x00 83FF                              | 0x00 8000 -><br>0x00 83FF   |  |

| 0x01           | 0x00 8400 -><br>0x00 87FF                  | 0x00 8400 -><br>0x00 87FF                    | 0x00 8400 -><br>0x00 87FF                    | 0x00 8400 -><br>0x00 87FF                              | 0x00 8400 -><br>0x00 87FF   |  |

| 0x02           | 0x00 8800 -><br>0x00 8BFF                  | 0x00 8800 -><br>0x00 8BFF                    | 0x00 8800 -><br>0x00 8BFF                    | 0x00 8800 -><br>0x00 8BFF                              | 0x00 8800 -><br>0x00 8BFF   |  |

| 0x03           | 0x00 8C00 -><br>0x00 8FFF                  | 0x00 8C00 -><br>0x00 8FFF                    | 0x00 8C00 -><br>0x00 8FFF                    | 0x00 8C00 -><br>0x00 8FFF                              | 0x00 8C00 -><br>0x00 8FFF   |  |

| 0x04           | 0x00 9000 -><br>0x00 93FF                  | 0x00 9000 -><br>0x00 93FF                    | 0x00 9000 -><br>0x00 93FF                    | 0x00 9000 -><br>0x00 93FF                              | 0x00 9000 -><br>0x00 93FF   |  |

| 0x05           | 0x00 9400 -><br>0x00 97FF                  | 0x00 9400 -><br>0x00 97FF                    | 0x00 9400 -><br>0x00 97FF                    | 0x00 9400 -><br>0x00 97FF                              | 0x00 9400 -><br>0x00 97FF   |  |

| 0x06           | 0x00 9800 -><br>0x00 9BFF                  | 0x00 9800 -><br>0x00 9BFF                    | 0x00 9800 -><br>0x00 9BFF                    | 0x00 9800 -><br>0x00 9BFF                              | 0x00 9800 -><br>0x00 9BFF   |  |

| 0x07           | 0x00 9C00 -><br>0x00 9FFF                  | 0x00 9C00 -><br>0x00 9FFF                    | 0x00 9C00 -><br>0x00 9FFF                    | 0x00 9C00 -><br>0x00 9FFF                              | 0x00 9C00 -><br>0x00 9FFF   |  |

| 0x08           | 0x00 A000 -><br>0x00 A3FF                  | 0x00 A000 -><br>0x00 A3FF                    | 0x00 A000 -><br>0x00 A3FF                    | 0x00 A000 -><br>0x00 A3FF                              | 0x00 1000 -><br>0x00 10FF   |  |

| 0x09           | 0x00 A400 -><br>0x00 A7FF                  | 0x00 A400 -><br>0x00 A7FF                    | 0x00 A400 -><br>0x00 A7FF                    | 0x00 A400 -><br>0x00 A7FF                              | -                           |  |

| 0x0A           | 0x00 A800 -><br>0x00 ABFF                  | 0x00 A800 -><br>0x00 ABFF                    | 0x00 A800 -><br>0x00 ABFF                    | 0x00 A800 -><br>0x00 ABFF                              | -                           |  |

| 0x0B           | 0x00 AC00 -><br>0x00 AFFF                  | 0x00 AC00 -><br>0x00 AFFF                    | 0x00 AC00 -><br>0x00 AFFF                    | 0x00 AC00 -><br>0x00 AFFF                              | -                           |  |

| 0x0C           | 0x00 B000 -><br>0x00 B3FF                  | 0x00 B000 -><br>0x00 B3FF                    | 0x00 B000 -><br>0x00 B3FF                    | 0x00 B000 -><br>0x00 B3FF                              | -                           |  |

| 0D             | 0x00 B400 -><br>0x00 B7FF                  | 0x00 B400 -><br>0x00 B7FF                    | 0x00 B400 -><br>0x00 B7FF                    | 0x00 B400 -><br>0x00 B7FF                              | -                           |  |

| 0x0E           | 0x00 B800 -><br>0x00 BBFF                  | 0x00 B800 -><br>0x00 BBFF                    | 0x00 B800 -><br>0x00 BBFF                    | 0x00 B800 -><br>0x00 BBFF                              | -                           |  |

| 0x0F           | 0x00 BC00 -><br>0x00 BFFF                  | 0x00 BC00 -><br>0x00 BFFF                    | 0x00 BC00 -><br>0x00 BFFF                    | 0x00 BC00 -><br>0x00 BFFF                              | -                           |  |

| 0x10           | 0x00 C000 -><br>0x00 C3FF                  | 0x00 C000 -><br>0x00 C3FF                    | 0x00 C000 -><br>0x00 C3FF                    | 0x00 C000 -><br>0x00 C3FF                              | -                           |  |

| 0x11           | 0x00 C400 -><br>0x00 C7FF                  | 0x00 C400 -><br>0x00 C7FF                    | 0x00 C400 -><br>0x00 C7FF                    | 0x00 C400 -><br>0x00 C7FF                              | -                           |  |

Table 9. STM8 sector codes (continued)

|                | Flash program memory/data EEPROM           |                                              |                                              |                                                        |                             |  |

|----------------|--------------------------------------------|----------------------------------------------|----------------------------------------------|--------------------------------------------------------|-----------------------------|--|

| Sector<br>code | STM8AF and<br>STM8S Series<br>high density | STM8AF and<br>STM8S Series<br>medium density | STM8L and<br>STM8AL Series<br>medium density | STM8L and<br>STM8AL Series<br>high/medium<br>+ density | STM8L Series<br>low density |  |

| 0x12           | 0x00 C800 -><br>0x00 CBFF                  | 0x00 C800 -><br>0x00 CBFF                    | 0x00 C800 -><br>0x00 CBFF                    | 0x00 C800 -><br>0x00 CBFF                              | -                           |  |

| 0x13           | 0x00 CC00 -><br>0x00 CFFF                  | 0x00 CC00 -><br>0x00 CFFF                    | 0x00 CC00 -><br>0x00 CFFF                    | 0x00 CC00 -><br>0x00 CFFF                              | -                           |  |

| 0x14           | 0x00 D000 -><br>0x00 D3FF                  | 0x00 D000 -><br>0x00 D3FF                    | 0x00 D000 -><br>0x00 D3FF                    | 0x00 D000 -><br>0x00 D3FF                              | -                           |  |

| 0x15           | 0x00 D400 -><br>0x00 D7FF                  | 0x00 D400 -><br>0x00 D7FF                    | 0x00 D400 -><br>0x00 D7FF                    | 0x00 D400 -><br>0x00 D7FF                              | -                           |  |

| 0x16           | 0x00 D800 -><br>0x00 DBFF                  | 0x00 D800 -><br>0x00 DBFF                    | 0x00 D800 -><br>0x00 DBFF                    | 0x00 D800 -><br>0x00 DBFF                              | -                           |  |

| 0x17           | 0x00 DC00 -><br>0x00 DFFF                  | 0x00 DC00 -><br>0x00 DFFF                    | 0x00 DC00 -><br>0x00 DFFF                    | 0x00 DC00 -><br>0x00 DFFF                              | -                           |  |

| 0x18           | 0x00 E000 -><br>0x00 E3FF                  | 0x00 E000 -><br>0x00 E3FF                    | 0x00 E000 -><br>0x00 E3FF                    | 0x00 E000 -><br>0x00 E3FF                              | -                           |  |

| 0x19           | 0x00 E400 -><br>0x00 E7FF                  | 0x00 E400 -><br>0x00 E7FF                    | 0x00 E400 -><br>0x00 E7FF                    | 0x00 E400 -><br>0x00 E7FF                              | -                           |  |

| 0x1A           | 0x00 E800 -><br>0x00 EBFF                  | 0x00 E800 -><br>0x00 EBFF                    | 0x00 E800 -><br>0x00 EBFF                    | 0x00 E800 -><br>0x00 EBFF                              | -                           |  |

| 0x1B           | 0x00 EC00 -><br>0x00 EFFF                  | 0x00 EC00 -><br>0x00 EFFF                    | 0x00 EC00 -><br>0x00 EFFF                    | 0x00 EC00 -><br>0x00 EFFF                              | -                           |  |

| 0x1C           | 0x00 F000 -><br>0x00 F3FF                  | 0x00 F000 -><br>0x00 F3FF                    | 0x00 F000 -><br>0x00 F3FF                    | 0x00 F000 -><br>0x00 F3FF                              | -                           |  |

| 0x1D           | 0x00 F400 -><br>0x00 F7FF                  | 0x00 F400 -><br>0x00 F7FF                    | 0x00 F400 -><br>0x00 F7FF                    | 0x00 F400 -><br>0x00 F7FF                              | -                           |  |

| 0x1E           | 0x00 F800 -><br>0x00 FBFF                  | 0x00 F800 -><br>0x00 FBFF                    | 0x00 F800 -><br>0x00 FBFF                    | 0x00 F800 -><br>0x00 FBFF                              | -                           |  |

| 0x1F           | 0x00 FC00 -><br>0x00 FFFF                  | 0x00 FC00 -><br>0x00 FFFF                    | 0x00 FC00 -><br>0x00 FFFF                    | 0x00 FC00 -><br>0x00 FFFF                              | -                           |  |

| 0x20           | 0x01 0000 -><br>0x01 03FF                  | 0x00 4000 -><br>0x00 43FF                    | 0x00 1000 -><br>0x00 13FF                    | 0x01 0000 -><br>0x01 03FF                              | -                           |  |

| 0x21           | 0x01 0400 -><br>0x1 07FF                   | -                                            | -                                            | 0x01 0400 -><br>0x1 07FF                               | -                           |  |

| 0x22           | 0x01 0800 -><br>0x01 0BFF                  | -                                            | -                                            | 0x01 0800 -><br>0x01 0BFF                              | -                           |  |

| 0x23           | 0x01 0C00 -><br>0x01 0FFF                  | -                                            | -                                            | 0x01 0C00 -><br>0x01 0FFF                              | -                           |  |

| 0x24           | 0x01 1000 -><br>0x01 13FF                  | -                                            | -                                            | 0x01 1000 -><br>0x01 13FF                              | -                           |  |

Table 9. STM8 sector codes (continued)

|                | Flash program memory/data EEPROM                                                        |   |                                                        |                             |   |  |

|----------------|-----------------------------------------------------------------------------------------|---|--------------------------------------------------------|-----------------------------|---|--|

| Sector<br>code | STM8AF and STM8AF and STM8L and STM8S Series high density medium density medium density |   | STM8L and<br>STM8AL Series<br>high/medium<br>+ density | STM8L Series<br>low density |   |  |

| 0x25           | 0x01 1400 -><br>0x01 17FF                                                               | - | -                                                      | 0x01 1400 -><br>0x01 17FF   | - |  |

| 0x26           | 0x01 1800 -><br>0x01 1BFF                                                               | - | -                                                      | 0x01 1800 -><br>0x01 1BFF   | - |  |

| 0x27           | 0x01 1C00 -><br>0x01 1FFF                                                               | - | -                                                      | 0x011C00 -><br>0x011FFF     | - |  |

| 0x28           | 0x01 2000 -><br>0x01 23FF                                                               | - | -                                                      | 0x01 2000 -><br>0x01 23FF   | - |  |

| 0x29           | 0x01 2400 -><br>0x01 27FF                                                               | - | -                                                      | 0x01 2400 -><br>0x01 27FF   | - |  |

| 0x2A           | 0x01 2800 -><br>0x01 2BFF                                                               | - | -                                                      | 0x01 2800 -><br>0x01 2BFF   | - |  |

| 0x2B           | 0x01 2C00 -><br>0x01 2FFF                                                               | - | -                                                      | 0x01 2C00 -><br>0x01 2FFF   | - |  |

| 0x2C           | 0x01 3000 -><br>0x01 33FF                                                               | - | -                                                      | 0x01 3000 -><br>0x01 33FF   | - |  |

| 0x2D           | 0x01 3400 -><br>0x01 37FF                                                               | - | -                                                      | 0x01 3400 -><br>0x01 37FF   | - |  |

| 0x2E           | 0x01 3800 -><br>0x01 3BFF                                                               | - | -                                                      | 0x01 3800 -><br>0x01 3BFF   | - |  |

| 0x2F           | 0x01 3C00 -><br>0x01 3FFF                                                               | - | -                                                      | 0x01 3C00 -><br>0x01 3FFF   | - |  |

| 0x30           | 0x01 4000 -><br>0x01 43FF                                                               | - | -                                                      | 0x01 4000 -><br>0x01 43FF   | - |  |

| 0x31           | 0x01 4400 -><br>0x01 47FF                                                               | - | -                                                      | 0x01 4400 -><br>0x01 47FF   | - |  |

| 0x32           | 0x01 4800 -><br>0x01 4BFF                                                               | - | -                                                      | 0x01 4800 -><br>0x01 4BFF   | - |  |

| 0x33           | 0x01 4C00 -><br>0x01 4FFF                                                               | - | -                                                      | 0x01 4C00 -><br>0x01 4FFF   | - |  |

| 0x34           | 0x01 1000 -><br>0x01 53FF                                                               | - | -                                                      | 0x01 1000 -><br>0x01 53FF   | - |  |

| 0x35           | 0x01 5400 -><br>0x01 57FF                                                               | - | -                                                      | 0x01 5400 -><br>0x01 57FF   | - |  |

| 0x36           | 0x01 5800 -><br>0x01 5BFF                                                               | - | -                                                      | 0x01 5800 -><br>0x01 5BFF   | - |  |

| 0x37           | 0x01 5C00 -><br>0x01 5FFF                                                               | - | -                                                      | 0x01 5C00 -><br>0x01 5FFF   |   |  |

Table 9. STM8 sector codes (continued)

|                | Flash program memory/data EEPROM           |                                              |                                              |                                                        |                             |  |

|----------------|--------------------------------------------|----------------------------------------------|----------------------------------------------|--------------------------------------------------------|-----------------------------|--|

| Sector<br>code | STM8AF and<br>STM8S Series<br>high density | STM8AF and<br>STM8S Series<br>medium density | STM8L and<br>STM8AL Series<br>medium density | STM8L and<br>STM8AL Series<br>high/medium<br>+ density | STM8L Series<br>low density |  |

| 0x38           | 0x01 6000 -><br>0x01 63FF                  | -                                            | -                                            | 0x01 6000 -><br>0x01 63FF                              | -                           |  |

| 0x39           | 0x01 6400 -><br>0x01 67FF                  | -                                            | -                                            | 0x01 6400 -><br>0x01 67FF                              | -                           |  |

| 0x3A           | 0x01 6800 -><br>0x01 6BFF                  | -                                            | -                                            | 0x01 6800 -><br>0x01 6BFF                              | -                           |  |

| 0x3B           | 0x01 6C00 -><br>0x01 6FFF                  | -                                            | -                                            | 0x01 6C00 -><br>0x01 6FFF                              | -                           |  |

| 0x3C           | 0x01 7000 -><br>0x01 73FF                  | -                                            | -                                            | 0x01 7000 -><br>0x01 73FF                              | -                           |  |

| 0x3D           | 0x01 7400 -><br>0x01 77FF                  | -                                            | -                                            | 0x01 7400 -><br>0x01 77FF                              | -                           |  |

| 0x3E           | 0x01 7800 -><br>0x01 7BFF                  | -                                            | -                                            | 0x01 7800 -><br>0x01 7BFF                              | -                           |  |

| 0x3F           | 0x01 7C00 -><br>0x01 7FFF                  | -                                            | -                                            | 0x01 7C00 -><br>0x01 7FFF                              | -                           |  |

| 0x40           | 0x01 8000 -><br>0x01 83FF                  | -                                            | -                                            | 0x00 1000 -><br>0x00 13FF                              | -                           |  |

| 0x41           | 0x01 8400 -><br>0x01 87FF                  | -                                            | -                                            | 0x00 1400 -><br>0x00 17FF                              | -                           |  |

| 0x42           | 0x01 8800 -><br>0x01 8BFF                  | -                                            | -                                            | -                                                      | -                           |  |

| 0x43           | 0x01 8C00 -><br>0x01 18FFF                 | -                                            | -                                            | -                                                      | -                           |  |

| 0x44           | 0x01 9000 -><br>0x01 93FF                  | -                                            | -                                            | -                                                      | -                           |  |

| 0x45           | 0x01 9400 -><br>0x01 97FF                  | -                                            | -                                            | -                                                      | -                           |  |

| 0x46           | 0x01 9800 -><br>0x01 9BFF                  | -                                            | -                                            | -                                                      | -                           |  |

| 0x47           | 0x01 9C00 -><br>0x01 9FFF                  | -                                            | -                                            | -                                                      | -                           |  |

| 0x48           | 0x01 A000 -><br>0x01 A3FF                  | -                                            | -                                            | -                                                      | -                           |  |

| 0x49           | 0x01 A400 -><br>0x01 A7FF                  | -                                            | -                                            | -                                                      | -                           |  |

| 0x4A           | 0x01 A800 -><br>0x01 ABFF                  | -                                            | -                                            | -                                                      | -                           |  |

Table 9. STM8 sector codes (continued)

|                | Flash program memory/data EEPROM           |                                              |                                              |                                                        |                             |  |

|----------------|--------------------------------------------|----------------------------------------------|----------------------------------------------|--------------------------------------------------------|-----------------------------|--|